中心議題:

- VDMOSFET的工作原理

- VDMOSFET的參數設計

- VDMOSFET的橫向結構設計

- VDMOSFET的仿真優化及器件研制結果分析

解決方案:

- VDMOSFET采用“5個場限環+鋁場板+多晶場板”的終端結構

隨著現代工藝水平的提高與新技術的開發完善,功率VDMOSFET設計研制朝著高壓、高頻、大電流方向發展,成為目前新型電力電子器件研究的重點。本文設計了漏源擊穿電壓為500 V,通態電流為8 A,導通電阻小于O.85 Ω的功率VDMOSFET器件,并通過工藝仿真軟件TSUPREM-4和器件仿真軟件MEDICI進行聯合優化仿真,得到具有一定設計余量的參數值。最后在此基礎上進行生產線工藝流片,逐步調整部分工藝條件,最終實現研制成功。

1 VDMOSFET工作原理

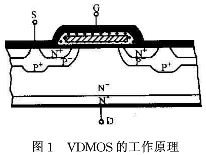

VDMOSFET是電壓控制器件,在柵極施加一定的電壓,使器件溝道表面反型,形成連接源區和漏區的導電溝道。基本工作原理如圖1。

當柵源電壓VGS大于器件的閾值電壓VTH時,在柵極下方的P型區形成強反型層,即電子溝道,此時在漏源電壓VDS的作用下,N+源區的電子通過反型層溝道,經由外延層(N-漂移區)運動至襯底漏極,從而形成漏源電流。

當VGS小于閾值電壓VTH時,柵極下方不能形成反型層溝道。由于外延層(N-漂移區)的濃度較低,則耗盡層主要在外延層(N-漂移區)一側擴展,因而可以維持較高的擊穿電壓。

2 VDMOSFET的參數設計

2.1 外延層電阻率和厚度

外延層的電阻率ρ越大(摻雜濃度Nepi越小),則器件的擊穿電壓越大。然而,導通電阻Ron也相應增大。因此,在滿足擊穿要求的前提下,ρ越小(Nepi越大)越好;而從導通電阻的角度考慮,又限定了該電阻率的最大值。所以將在計算機仿真過程中,調整P-body的注入劑量、推阱時間和外延層電阻率、厚度,得出最佳的結構參數。

2.2 閾值電壓

影響閾值電壓的因素主要是P-body濃度NA,柵氧化層厚度tox和柵氧化層的面電荷密度Qss,主要通過調整P阱注入劑量和推阱時間來調節閾值電壓Vth。

此外,柵氧化層厚度tox受柵源擊穿電壓的限制,tox≥VGS/EB,SiO2的臨界電場EB一般為5×106~107 V/cm;由此算得tox的值為30 nm~60 nm;由于P-body為非均勻摻雜,VTH難于用公式準確計算,因此柵氧化層厚度tox和pbody濃度的最佳值需借助于計算機仿真優化來確定。

2.3 導通電阻

對于功率VDMOSFET器件,在不同耐壓下,各部分電阻占導通電阻的比例是不同的。對于高壓VDMOSFET器件,漂移區(外延層)電阻RD和JFET區電阻RJ是主要的。

因此,本設計在滿足耐壓的情況下,采用穿通型結構,以減小外延層厚度,并適當增加JFET區的寬度,從而減小RD與RJ。

2.4 開關時間

優化開關時間的方法包括兩個方面:減小多晶硅柵的電阻RG和減小輸入電容Cin。在輸入電容中,密勒電容CGD是主要的影響因素。

減小多晶硅的電阻RG可以在工藝過程中提高多晶硅的摻雜劑量,在版圖設計過程中增加柵極多晶硅與柵極鋁引線的接觸孔;減小輸入電容Cin主要是減小密勒電容CGD,即要增加柵氧化層厚度tox,這會加大閾值電壓VTH,因而需要折中考慮。

[page]

3 VDMOSFET的橫向結構設計

3.1 元胞結構選取

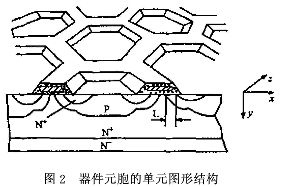

由于正三角形元胞的電場容易集中,導致漏源擊穿電壓的降低;六角形元胞的對角線與對邊距的比值為,小于方形元胞的對角線與邊長的比值,電流分布的均勻性好,曲率效應小;圓形元胞犧牲率(即A’/Acell,其中A’為元胞邊緣結合處電流不能流過的無效區面積,Acell為元胞總面積)大于六角形元胞。

因此,本文所設計的500 V高壓VDMOSFET器件采用正六角形“品”字排列的元胞結構。

3.2 柵電極結構

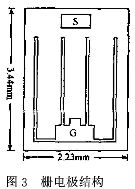

功率VDMOSFET由很多小元胞單元并聯組成。而由于柵極多晶硅電阻的存在,使得在一定的柵極偏壓下,離柵極壓焊點較遠的元胞溝道不能充分開啟。因此,為了降低柵電極材料電阻的影響,通常將柵極壓焊點處的金屬引伸到離壓焊點較遠的元胞單元處。本文所設計的功率管從壓焊點處引伸3條金屬條并與下面的多晶硅相接觸。

3.3 結終端結構設計

傳統的場板與場限環相結合的結終端結構如圖3所示。設計時,如果場板和保護環的間距過大,場板下的耗盡層擴展到保護環之前PN結就首先擊穿,保護環將起不到作用。

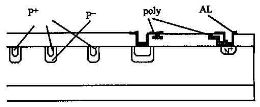

本文研究的新型結終端結構(如圖4所示),是采用場板覆蓋保護環的方式,避免了傳統場板與場限環結構的設計難題,而使其簡單化。

圖4 場板與場限環結合的新結構

這種結構在版圖設計上通過增加鋁場板的長度來實現,比較容易控制,使得金屬覆蓋過離主結最近的場限環,它不僅起到了場板和場限環的效果,又避免了傳統結構在場板的邊緣產生新的電場峰值,避免了電壓在場板邊緣和場限環之間的提前擊穿。

[page]

4 仿真優化結果

本設計采用“5個場限環+鋁場板+多晶場板”的終端結構,通過工藝仿真軟件TSUPREM-4和器件仿真軟件MEDICI進行聯合仿真,不斷調整工藝參數,優化元胞和結終端結構,最終使各項參數的仿真指標滿足設計要求。

5 器件研制結果分析

本產品研制按照功率VDMOSFET正向設計的思路,選取<100>晶向的襯底硅片,采用硅柵自對準工藝流程,首次流片遵照計算機仿真優化的工藝條件,進行工藝摸底;針對測試結果,逐步進行局部工藝調整,最終使得產品指標滿足設計要求。

(1)第一次流片

產品測試結果表明:產品的擊穿電壓均值為438.82 V,并且普遍低于設計要求的500 V。

經分析,其可能存在的原因是:由于襯底反擴散較大,從而導致外延層電阻率偏低,使得擊穿電壓降低。因此,在第二次流片時,將外延電阻率提高5 Ω·cm,其它工藝條件保持不變。

(2)第二次流片

測得的擊穿電壓平均值551.68 V,大于500 V,滿足設計要求。然而,隨著外延層電阻率的提高,部分導通電阻已大于設計要求的850 mΩ。

改進方案:對于高壓功率VDMOSFET器件,JFET電阻在導通電阻的組成部分中,占有相對較大的比重。因此,在擊穿電壓余量充分的條件下,可考慮通過適當減小P-body推結時間的方法,從而增加兩相鄰P-body的間距,降低JFET電阻。因此,在第三次投片時,將P-body的推結時間調減20分鐘,其它工藝條件相對于第二次流片保持不變。

(3)第三次流片

測試結果表明:在減小P-body推結時間后,導通電阻小于850 mΩ,滿足設計要求;雖然產品的擊穿電壓(均值536 V)有所下降,但仍滿足大于500 V的設計要求;其余靜態參數、動態參數指標也均滿足設計要求。

因此認為,本文高壓功率VDMOSFET的器件設計與研制工作是成功的。

6 結束語

本文在計算機仿真優化的基礎上,通過對產品測試結果的分析及工藝條件的調整,最終實現了成功研制。相對于傳統的流水線小批量投片、反復試制的方法大大節約了研制成本,收到了事半功倍的效果。

隨著半導體生產制造工藝的不斷改進,器件模擬和工藝模擬的精度與實際工藝流程的吻合性將越來越好,使產品的模擬結果更具有實用性、可靠性。