中心議題:

- USB3.0 五分頻電路原理與結構

- USB3.0 分頻器基本電路的設計

USB 3. 0 是通用串行總線( Universal Serial Bus)的最新規范, 該規范由英特爾等大公司發起, 其最高傳輸速度可達5 Gb/ s,并且兼容USB 2. 0 及以下接口標準。物理層的并串/ 串并轉換電路是U SB 3. 0 的重要組成部分, 在發送端將經過8 b/ 10 b 編碼的10 位并行數據轉換成串行數據并傳輸到驅動電路, 在接收端將經過CDR( Clock and Data Recovery) 恢復出來的串行數據轉換成10 位并行數據。在并串/ 串并轉換過程中,同時存在著時鐘頻率的轉換, 若串行數據采用時鐘上下沿雙沿輸出,則串行數據傳輸頻率降低一半, 并行傳輸時鐘為串行傳輸時鐘的1/ 5, 即五分頻。

本文設計了基于65 nm 工藝的五分頻器, 產生一個占空比為50%的五分頻信號。對該電路的設計不以追求高速度為惟一目標,而是在滿足U SB 3. 0 協議所要求的頻率范圍基礎上, 盡可能的降低功耗。

1 電路原理與結構

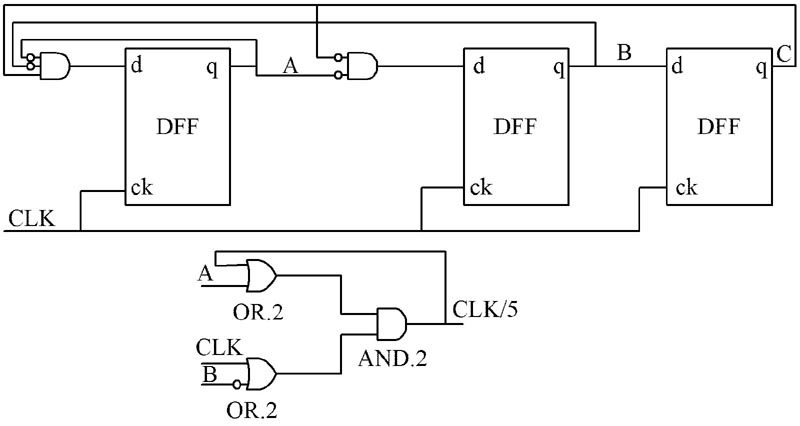

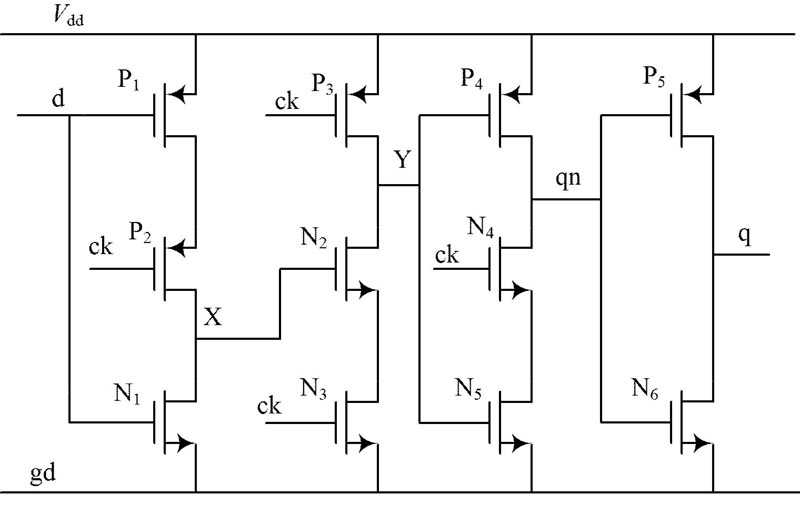

采用基于D 觸發器結構的五分頻器邏輯框圖如圖1所示。圖1 由3 個D 觸發器和少量邏輯門構成, 采用了同步工作模式, 其原理是由吞脈沖計數原理產生2 個占空比不同的五分頻信號A 和B, 然后對時鐘信號CLK, A 和B 進行邏輯運算得到占空比為50% 的五分頻信號CLK/ 5, 其計數過程如表1 所示, 從表1 的計數過程可知, 分頻后的時鐘CLK/ 5 的周期是輸入時鐘CLK 的5 倍, 由此實現了五分頻并且其占空比為50% .

圖1 5 分頻電路邏輯結構

表1 5 分頻器計數過程[page]

2 分頻器基本電路的設計

觸發器是整個分頻器中最基本的結構, 只有設計好一個快速的觸發器, 才能實現一個高頻率的分頻器,目前用于分頻電路的觸發器電路主要有3 種。第1 種是CML( Current Mo de lo gic) 電路, 是由ECL( EmitterCo uple Logic) 電路演變來的, 相比傳統的靜態分頻器,由于電路的擺幅較小, 因而電路的工作速度快; 第2 種是TSPC( True Single Phase Clock) 電路, 采用單相時鐘, 大大減少了電路的元件數目, 從而提高電路工作速度, 同時這種電路功耗極低; 第3 種是注鎖式( Injected-Locked) 電路, 由于要使用電感, 因而它的體積過大且工藝難度高, 成本較高, 很少被廣泛采用。本文分別采用CML 電路和TSPC 電路構成分頻電路, 并對兩者的速度和功耗等進行比較。

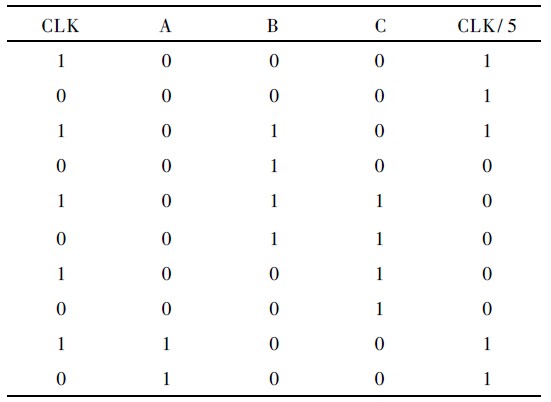

CML 電路構成的觸發器如圖2 所示, 由圖中可以看出, 該觸發器由2 個CML 結構鎖存器組成, 它們構成主從型結構, 每個鎖存器都要經過2 個階段: 跟蹤階段和保持階段。當主鎖存器跟蹤輸入信號時, 從鎖存器處于鎖存保持階段, 然后交替。其中N13 , N14 為尾電流管, 偏置電壓V_bias 使N13 , N14管工作在飽和狀態, 充當恒流源的作用。dp 和dn 是由輸入信號d 經傳輸門和反相器產生的一對互補差分信號, ck_m 和ck_p 是由輸入時鐘信號clk 經傳輸門和反相器產生的一對互補時鐘差分信號。主鎖存器工作狀態為: 當ck_m 為高電平時, N5 管導通, N6 管關閉, 此時N1 , N2 管工作在差分狀態, 將輸入信號dp, dn 采入。當ck_p 為高電平時,N6 管導通, N5 管關閉, 此時N3 , N4 使電路維持在鎖存狀態, 從鎖存器工作狀態恰好與主鎖存器工作狀態相反。設計中在觸發器輸出端q, qn 之間加了2 個反相器從而在q, qn 之間形成正反饋, 增強了電路的輸出驅動能力。工作時, 電路的尾電流應當足夠大, 有利于提高電路工作頻率和輸出信號的擺幅。

圖2 CML 鎖存器構成的主從式觸發器電路

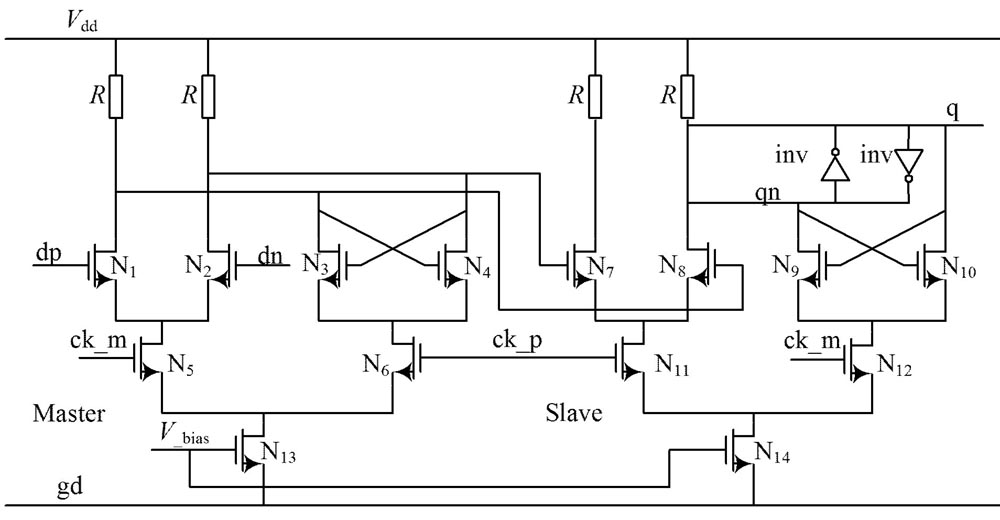

TSPC 電路構成的觸發器如圖3 所示, 由圖中可以看出, 該電路由四級反相器構成, 上升沿觸發, 當CK 為低電平, 輸入反相器在節點X 上采樣反向d 輸入,第2 級反相器處于保持狀態, 節點Y 預充電至V dd,第三級反相器處于保持狀態, 時鐘上升沿來時, 第二級反相器求值, Y 的電平值發生變化, 時鐘ck 為高電平時,節點Y 的值傳送到輸出q, 該觸發器的延時為4 個反相器的傳播延時, 由于電路中元件數目很少, 而且采用動態邏輯, 因此功耗極低。

圖3 TSPC 電路構成的觸發器[page]

3 仿真結果與分析

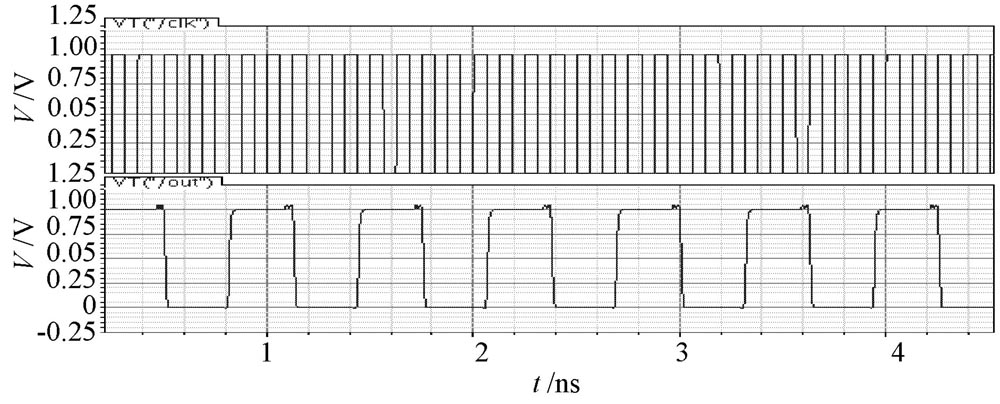

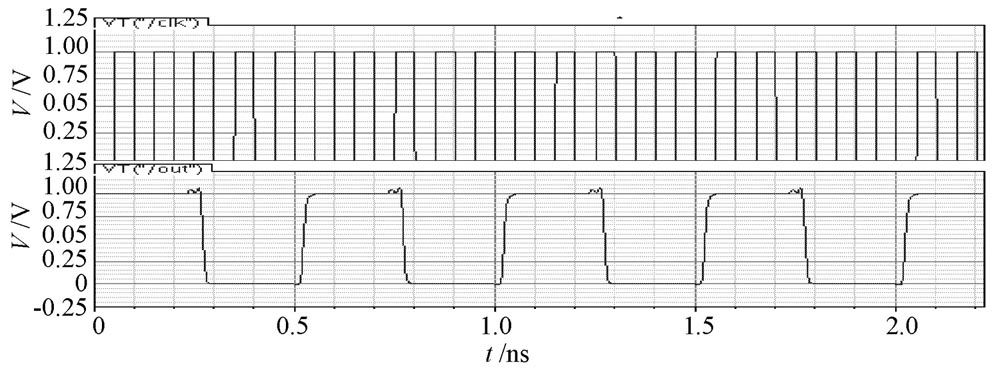

采用Cadence 公司的spect re 仿真器對設計的分頻器分別仿真, 仿真電源電壓為1 V, 結果表明: 在典型工藝參數條件下,基于CML 電路結構的五分頻器最大工作頻率是8 GHz, 最小工作頻率是1 kHz, 當工作在8 GHz 時, 功耗為1. 7 mW, 輸出信號占空比為49. 76% ; 基于T SPC 電路結構的五分頻器最大工作頻率是10 GHz, 最小工作頻率是10 MHz, 當工作在10 GH z時, 功耗采用10 ns 內的平均功耗, 功耗為0. 2 mW, 輸出信號占空比為49. 92%.由于是單端輸入輸出, 基于T SPC 電路結構的分頻器抗噪聲能力較弱。最高工作頻率下的仿真結果如圖4, 圖5 所示。

圖4 基于CML 電路結構的五分頻器工作在8 GH z 仿真圖

圖5 基于T SPC 電路結構的五分頻器工作在10 GHz 仿真圖

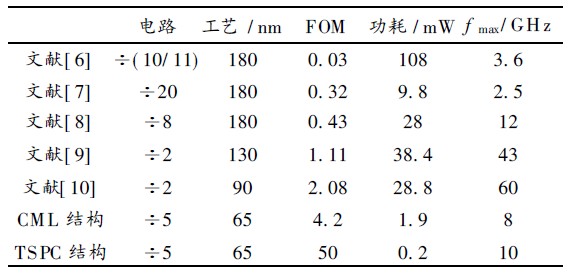

對于不同頻率的分頻器。通常采用FOM 值來比較其性能, 分頻器的FOM 值定義為:

![]()

式中: fmax 是分頻器的最高工作頻率; P 是分頻器在最高工作頻率下的功耗, 表2 為本文設計的分頻器和其他文獻中介紹的分頻器作對比,所有的分頻器均采用CMOS工藝, 對比表明本文設計的5 分頻器性能較優,在65 nm 工藝下具有明顯的功耗低優勢, 尤其是采用TSPC 電路結構的分頻器, 功耗極低。

表2 幾種分頻器性能的總結對比

4 結語

本文基于65 nm 工藝分別采用CML 電路結構和TSPC 電路結構設計了1 個五分頻器, 采用spectr e 仿真表明, 采用CML 結構的分頻器最高工作頻率8 GHz,功耗1. 7 mW, 輸出信號占空比49. 76% ; 采用T SPC 電路結構分頻器最高工作頻率10 GHz, 功耗為0. 2 mW,輸出信號占空比49. 91%, 由于采用單端輸入輸出, 所以采用T SPC 結構的分頻器抗噪聲能力較弱。輸出信號占空比為50% 是本文一大特點, 2 種結構的分頻器工作頻率完全覆蓋了U SB 3. 0 協議所要求的頻率范圍,滿足協議要求。